# High CMR Isolated 6SW 2A Smart Gate Drive Module For SiC FETs

#### **Applications**

- 6 Switch Isolated

SiC/IGBT/MOSFET Gate

Driver

- AC & Brushless DC Motor Drives

- 3 Phase PFC Rectifiers

- R&D Inverters

#### Compliance

ROHS

#### **Features**

- Best Cost to Performance Ratio in the Market.

- Suitable for 1200V SiC FET, IGBTs & MOSFETs up-to 120A.

- 2A Peak Gate Drive Current.

- 3000 V<sub>RMS</sub> Input to Output Isolation.

- Short-Circuit Protection Through Desaturation Detection.

- Active Miller Protection.

- Output UVLO Protection.

- Output Clamping Protection.

- Isolated Fault Feedback.

- Soft Turnoff in Case of Fault.

- Fault Latch Shutdown.

- Configurable PWM/Dual Inputs.

- Configurable Dead-Time.

- 100KV/us Minimum Common Mode Rejection (CMR).

- Very Low Propagation Delay of 110ns (Maximum) for High Frequency Operation.

- Input & Output Indication LEDs for Visual Feedback.

- Input & Output Test points for easy testing.

- Built-in 5V Regulator for Powering up External Control Circuitry.

#### Description

The GDC-2A6S1 is high performance fully isolated SiC/IGBT/MOSFET gate drive module for 6 Switches. It is specially designed for fastest inverter prototyping in research and educational environments. The drive use's Texas Instrument's ISO5852 smart and high performance gate driver IC, and feature's dead time generation logic, fault latch logic, input and output indication LEDs, test points and built in 5V regulator which could be used to power up external control circuitry.

But the most notable feature of this module is that it detects short circuit condition using desaturation detection and can safely turn off the switch and give the controller an isolated fault feedback signal. Another major feature of GDC series is very high common mode immunity of 100 kV/us. Due to very high switching speeds of SiC FETs, high immunity is required for proper operation of the gate driver module.

This product can be ordered with different output voltages suitable for different available SiC FETs in the market. Available options are +20/-5, +18/0, +15/0, +15/-5 & +15/-15.

#### DATASHEET

#### **Revision History Table**

| Version | Release Date | Changes                         |

|---------|--------------|---------------------------------|

| 1.0     | 19/06/2019   | First Version Released          |

| 1.1     | 3/09/2019    | Application information updated |

## WARNING AND DISCLAIMER !

ATTENTION PLEASE! THE INFORMATION HEREIN IS GIVEN TO DESCRIBE CERTAIN COMPONENTS AND SHALL NOT BE CONSIDERED AS A GUARANTEE OF CHARACTERISTICS. TERMS OF DELIVERY AND RIGHTS TO TECHNICAL CHANGE RESERVED. WE HEREBY DISCLAIM ANY AND ALL WARRANTIES, INCLUDING BUT NOT LIMITED TO WARRANTIES OF NON-INFRINGEMENT, REGARDING CIRCUITS, DESCRIPTIONS AND CHARTS STATED HEREIN. CUSTOMER IS SOLELY RESPONSIBLE OF PROPER AND LEGAL USE OF ALL PRODUCTS OFFERED BY TARAZ TECHNOLOGIES.

## **SAFETY NOTICE!**

ATTENTION PLEASE! THIS DEVICE IS ESD SENSITIVE AND NEEDS TO BE HANDLED WITH CARE. HIGH VOLTAGE CONDITION MAY OCCUR DURING OPERATION OF THE DEVICE, AND HENCE USER IS SOLELY RESPONSIBLE OF EQUIPMENT AND PERSONNEL SAFETY. TARAZ TECHNOLOGIES SHALL NOT BE HOLD LIABLE FOR ANY DAMAGE TO PERSONNEL AND/OR PROPERTIES AS A RESULT OF USING THIS DEVICE. USER MUST TAKE ADEQUATE STEPS TO ENSURE ELECTRICAL AND MECHANICAL SAFETLY OF THE DEVICE IN USE.

### DATASHEET

#### **Table of Contents**

| Features                                             | 1 |

|------------------------------------------------------|---|

| Applications                                         | 1 |

| Description                                          | 1 |

| Compliance                                           | 1 |

| Revision History Table                               |   |

| WARNING AND DISCLAIMER !                             | 2 |

| SAFETY NOTICE !                                      |   |

| Table of Contents                                    | 3 |

| Ratings & Characteristics                            |   |

| Block Diagram                                        |   |

| Pin Description                                      |   |

| Application Information                              |   |

| Typical Application Circuit                          | 8 |

| Operation Requirements                               | 8 |

| Power Supply & Configuration (J1 & J4)               | 8 |

| Output Connection (J7-J14)                           | 8 |

| Fault Latch Reset                                    | 8 |

| Operation Modes (S3)                                 | 9 |

| Configurable Dead Time (DT ADJ) in PWM Mode          | 9 |

| Selecting Appropriate Output Voltage for SiC Devices | 9 |

| Input & Output Indication LEDs, Test Points          | 9 |

| Mounting and Safety                                  | 9 |

| Mechanical Drawing                                   |   |

| Ordering Information                                 |   |

| Output Connectors                                    |   |

# **Ratings & Characteristics**

\*All ratings are given at Vs=15V and 25°C ambient temperature unless otherwise specified.

| Absolute Maximum Ratings                                  | Test Conditions/ Note         |            | Value      |     | Unit |

|-----------------------------------------------------------|-------------------------------|------------|------------|-----|------|

| Supply Voltage (V <sub>5</sub> )                          |                               | 18         |            | V   |      |

| Input Signal Voltage HIGH                                 |                               | 5.5        |            | V   |      |

| Input Signal Voltage LOW                                  |                               | 0          |            | V   |      |

| $Output Peak Current (I_{out(PEAK)}) Using Rg < 10\Omega$ |                               | 2          |            | А   |      |

| Output Power (Pout) Per Channel                           |                               | 1          |            | W   |      |

| Active Miller Clamp Current                               |                               | 1.6        |            | А   |      |

| Maximum Working Insulation Voltage                        | Vpeak                         |            | 1200       |     | V    |

| Input to Output Isolation                                 | AC RMS                        |            | 3000       |     | V    |

| J1 5V Output Current (Ioutsv)                             | Supply for external circuit   | 180        |            | mA  |      |

| Operating Temperature                                     | $I_{OUT5V} = 0$               | -25 to +70 |            | °C  |      |

| Storage Temperature                                       |                               |            | -25 to +85 |     | °C   |

| Recommended Operating Conditions                          | Test Conditions/ Note         | Minimum    | Typical    | Max | Unit |

| Supply Voltage (Vs)                                       |                               | 13         | 15         | 17  | V    |

| Supply Current                                            |                               |            | 100        | 300 | mA   |

| Operating temperature                                     | Ι <sub>ΟUT5V</sub> = 0        | -10        | -          | 70  | °C   |

| Input Signal Voltage On/Off                               | 3.3V control signals possible |            | 5/0        |     | V    |

# DATASHEET

# **Ratings & Characteristics (Continued)**

\*All ratings are given at Vs=15V and 25°C ambient temperature unless otherwise specified.

| Characteristics                     | Test Conditions/ Note                                                   | Minimum   | Typical          | Max      | Unit  |

|-------------------------------------|-------------------------------------------------------------------------|-----------|------------------|----------|-------|

| Logic High Input Threshold          |                                                                         | 2.0       | -                | -        | V     |

| Logic Low Input Threshold           |                                                                         | -         | -                | 0.8      | V     |

| Output Voltage (+20/-5 option)      | $V_{\text{S}} = 15V, 20mA \ I_{\text{out}(\text{AVG})}$                 | -5        |                  | 20       | V     |

| Output Voltage (+18/0 option)       | $V_{S}=15V,20mA\;I_{\text{out}(AVG)}$                                   | 0         |                  | 18       | V     |

| Output Voltage (+15/0 option)       | $V_{S}=15V,20mA\;I_{\text{out}(AVG)}$                                   | 0         |                  | 15       | V     |

| Output Voltage (+15/-5 option)      | $V_{\text{S}} = 15V, 20mA \ I_{\text{out}(\text{AVG})}$                 | -5        |                  | 15       | V     |

| Output Voltage (+15/-15 option)     | $V_{\text{S}} = 15V, 20mA \; I_{\text{out}(\text{AVG})}$                | -15       |                  | 15       | V     |

| Output UVLO Threshold               | UVLO +<br>UVLO -                                                        | 12<br>9.5 |                  | 13<br>11 | V     |

| Output Clamp Threshold              | Of Bi-directional TVS @ 1mA                                             | 22.2      | -                | 24.5     | V     |

| Fault Output Voltage                | Active LOW                                                              | -         | -                | 0.8      | V     |

| Input Impedance                     | All inputs have 22 kΩ pull-down resistors                               | -         | 22               | -        | kΩ    |

| Internal Gate to Emitter Resistance |                                                                         | -         | 6.2              | -        | kΩ    |

| Duty Cycle Range                    |                                                                         | 0         | -                | 100      | %     |

| Configurable Dead-time              | Using DT-ADJ                                                            | 0.58      | -                | 9.28     | us    |

| Propagation Delay                   | $R_g=10\Omega$ , $C_g=10nF$ , f=10kHz, Duty<br>Cycle = 50%              |           | 76               | 110      | ns    |

| Output Rise and Fall Time           | R <sub>g</sub> =10Ω, C <sub>g</sub> =10nF, f=10kHz, Duty<br>Cycle = 50% | 12        | 20               | 37       | ns    |

| DESAT Threshold                     |                                                                         | 8.3       | 9                | 9.5      | V     |

| Common Mode Rejection (CMR)         | At V <sub>CM</sub> =1500V                                               | 100       | 120              |          | kV/us |

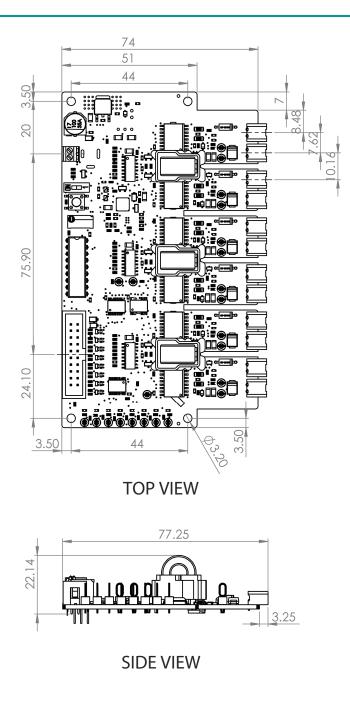

| Weight                              |                                                                         | -         | 59               | -        | g     |

| Dimensions (Bare)                   | Width x Length x Depth                                                  |           | 74 x 127 x 22.14 |          | mm    |

|                                     |                                                                         |           |                  |          |       |

DATASHEET

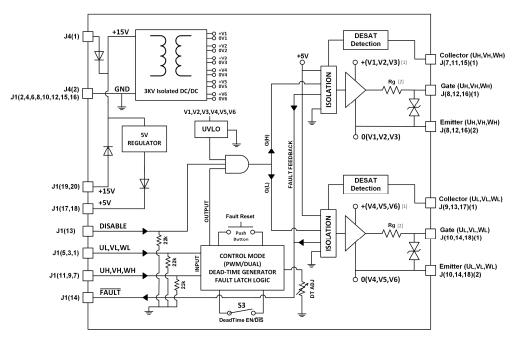

#### **Block Diagram**

Figure 1: Block Diagram

#### Notes:

- 1) All drivers are powered by isolated (floating) voltage sources.

- 2) The default gate resistor is 10Ω and user can control the gate turn on and off by changing Rg to lower value for faster switching, or higher value to minimize ringing. However, the minimum value to be used should be greater than or equal to SiC/IGBT/MOSFET datasheet recommended value for reliable operation.

- 3) In case of PWM mode, control signals will be generated from UH, VH & WH. User don't have to supply the UL, VL & WL signals.

### DATASHEET

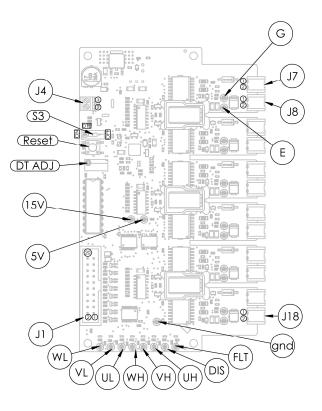

### **Pin Description**

| Name             | Connector (Pin No.)            | Description                                                                                                                                                                                                 |

|------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UH, VH, WH       | J1(11,9,7)                     | Non-inverting logic input terminal for HIGH side gate.                                                                                                                                                      |

| UL, VL, WL       | J1(5,3,1)                      | Non-inverting logic input terminal for LOW side gate. (Dual mode only)                                                                                                                                      |

| GND              | J4(2), J1(2,4,6,8,10,12,15,16) | Ground                                                                                                                                                                                                      |

| +15V             | J4(1), J1(19,20)               | +15V supply voltage (Vs) for the module. It can be supplied either from J4 or J1.                                                                                                                           |

| +5V              | J1(17,18)                      | +5V supply output from the module to power up the external circuit.                                                                                                                                         |

| DISABLE          | J1(13)                         | Input disable signal, active high will drive all outputs to LOW.                                                                                                                                            |

| FLT              | J1(14)                         | Fault feedback output, active low. When a fault condition occurs, this pin will move into low state.                                                                                                        |

| Collector        | J(7,9,11,13,15,17)(1)          | Output to SiC/IGBT/MOSFET collector terminal (must be connected).                                                                                                                                           |

| NC               | J(7,9,11,13,15,17)(2)          | This pin is not connected.                                                                                                                                                                                  |

| Gate             | J(8,10,12,14,16,18)(1)         | Output to SiC/IGBT/MOSFET gate terminal.                                                                                                                                                                    |

| Emitter          | J(8,10,12,14,16,18)(2)         | Output to SiC/IGBT/MOSFET emitter terminal.                                                                                                                                                                 |

| Reset            | Push Button                    | Once fault is triggered, it can either be reset with the reset push button, or by disabling the module using J1.13 and re-enable it after minimum 10us delay.                                               |

| PWM / Dual       | S3                             | Operation mode can be selected by turning dead-time ON (PWM mode) or OFF (Dual mode). If position 1 of switch S3 is at ON state then PWM mode is selected. Conversely, at OFF state, Dual Mode is selected. |

| Dead-Time Adjust | DT-ADJ                         | Duration of Dead-time can be adjusted by DT-ADJ potentiometer.                                                                                                                                              |

DATASHEET

#### **Application Information**

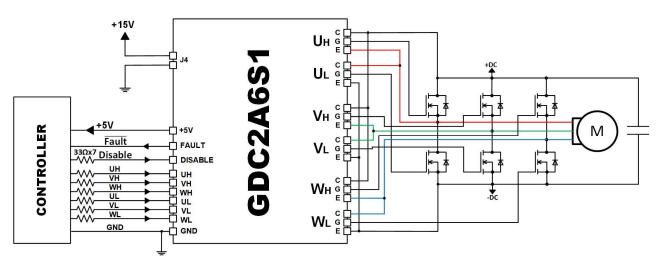

**Typical Application Circuit**

*Figure 2: Typical application circuit*

#### **Operation Requirements**

For proper operation of the gate drive module, certain requirements need to be fulfilled. First, the module need to be supplied with +15V voltage source through J4 or J1 connectors. Second, **all switches need to be connected including collector terminals**, failure to do so will latch the fault circuitry and module will become un-operational. Last, control signals need to be given to the module with recommended 33 Ohm transmission resistors to avoid ringing and noise. Disable signal must be in low state, while Fault signal can be monitored for feedback.

#### Power Supply & Configuration (J1 & J4)

Supply voltage (+15V) is provided through J4 terminal block. It can also be supplied from J1 (pins 19, 20). Moreover, user can utilize 5V supply from J1 (pins 17, 18) to power external control circuit.

#### **Output Connection (J7-J18)**

Output connectors from J7 to J18 should be directly connected to power switches accordingly. Please note that voltage difference between the collector and rest of output is high, and hence proper wiring and insulation must be used. Gate and emitter wires are recommended to be in twisted pairs in case of free hanging connectors and must be as short as possible.

#### **Fault Latch Reset**

Fault output pin (J1.14) indicates fault condition at any switch and is active LOW. Once fault is detected, the output will be muted for  $5\mu s$  (minimum). Any input signal will be ignored during this mute period to allow driver to completely soft shut-down the switch.

Fault will be triggered by either desaturation detection or wiring disconnection. Once fault is triggered, it can either be reset with the push button, or by disabling the module using J1.13 (Disable) and re-enable it after minimum 10us delay. The module will resume operation after fault is cleared.

# **Application Information (Continued)**

### **Operation Modes (S3)**

User can select to use this gate driver as PWM or Dual input mode using S3. All gate driver modules are preconfigured in PWM mode by default. In PWM mode (S3 ON State), UL, VL and WL signals are generated by deadtime generation logic. The user has to connect only UH, VH and WH signals to Input. In Dual mode (S3 OFF State), all channels are independently controlled through respective signals, this is required for some topologies where shoot-through is needed such as Z-Source Inverter.

### Configurable Dead Time (DT ADJ) in PWM Mode

User can configure the internal dead time using DT ADJ potentiometer. The duration of dead time delay DT can be calculated as per equation 1.

$DT \approx 0.39579 \ x \ RDT$

#### Equation 1.

Where: DT= dead time ( $\mu$ s), and RDT= on board dead time programming trimmer ( $k\Omega$ ), which varies from 1k to 21k $\Omega$ , changing dead time from 0.39579 $\mu$ s to 8.3 $\mu$ s. By default, the module is configured at 2.2 $\mu$ s dead time. If dead time need to be adjusted, it must be done with switches high voltage power supply in OFF condition.

### Selecting Appropriate Output Voltage for SiC Devices

Due to variety of available SiC devices in the market, gate drive voltage requirements of each SiC device varies greatly, choosing the correct voltage is important for reliable operation of the switch and gate driver. Following are examples of different series SiC devices with recommended gate drive voltages.

| SiC Series | Manufacturer | Output Voltage | Also Use for    |

|------------|--------------|----------------|-----------------|

| C3M        | Cree         | +15V/-5V       | IGBTs & MOSFETs |

| C2M        | Cree         | +20V/-5V       |                 |

| SCT        | Rohm         | +18V/0V        |                 |

### Input & Output Indication LEDs, Test Points

LEDs are provided on input and output signals for instant user feedback. Input side LEDs are yellow colored. While output LEDs are independent for ON (Orange) state and OFF (Yellow) state so user can have feedback of high frequency PWM signals as well. Separate LEDs also indicate DISABLE (Orange), FAULT (RED) and Power state (Green).

The module also has input and output test points for easy debugging. This is very helpful feature for educational and research use. Test points are available on all inputs, Disable, Fault, Power (+15V, +5V, GND) and Gate, Emitter of all outputs.

#### Mounting and Safety

Since output side may carry dangerous high voltage, it is not safe to touch the circuit in operation. User must consider proper clearance of heat sink, metal enclosure, stray metallic objects near output side, and cover module and inverter with proper insulated casing. Care must be taken with mounting since mounting holes are close to outputs.

#### **Mechanical Drawing**

#### Notes:

\* All dimensions are in mm.

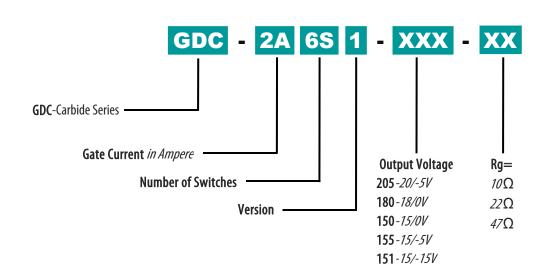

#### **Ordering Information**

#### Notes:

The default gate resistor is 10Ω. However, user can control gate turn on and off speed by changing Rg to a lower value for faster switching or higher value to minimize ringing effect. The minimum value to be used should be greater than or equal to SiC/IGBT/MOSFET datasheet recommended value for reliable operation.

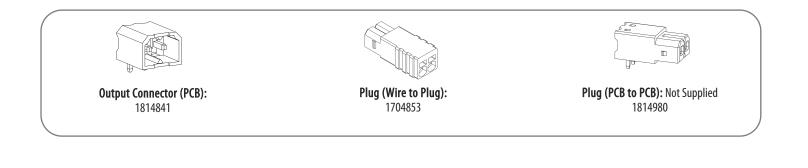

#### **Output Connectors**

For Further information or purchasing, please go to our web site:

www.taraztechnologies.com

Address: 21-X, 2nd Floor, DHA Business Avenue, DHA Phase 1, Bahria Expressway, Rawalpindi 46000, Pakistan Phone: +92 (51) 5400335 Fax: +92 (51) 5400155 E-Mail: info@taraztechnologies.com Data subject to change. Copyright © 2019 Taraz Technologies. All rights reserved.